# Section 35. Output Compare with Dedicated Timer

# HIGHLIGHTS

This section of the manual comprises the following major topics:

| 35.1  | Introduction                                    |  |

|-------|-------------------------------------------------|--|

| 35.2  | Output Compare Registers                        |  |

| 35.3  | Modes of Operation                              |  |

| 35.4  | Output Compare Operation in Power-Saving States |  |

| 35.5  | I/O Pin Control                                 |  |

| 35.6  | Register Maps                                   |  |

| 35.7  | Electrical Specifications                       |  |

| 35.8  | Design Tips                                     |  |

| 35.9  | Related Application Notes                       |  |

| 35.10 | Revision History                                |  |

# 35.1 INTRODUCTION

The output compare module in PIC24F devices compares the Timer register value with the value of one or two Compare registers, depending on its mode of operation. The output compare module on compare match events has the ability to generate a single output transition or a train of output pulses. Like most PIC<sup>®</sup> MCU peripherals, the output compare module can also generate interrupts on a compare match event.

Each output compare timer can use one of the available six selectable time clocks. The clock is selected using the OCTSEL<2:0> (OCxCON1<12:10>) bits. Refer to the applicable device data sheet for more information about specific timers that can be used as a time base for the output compare timer.

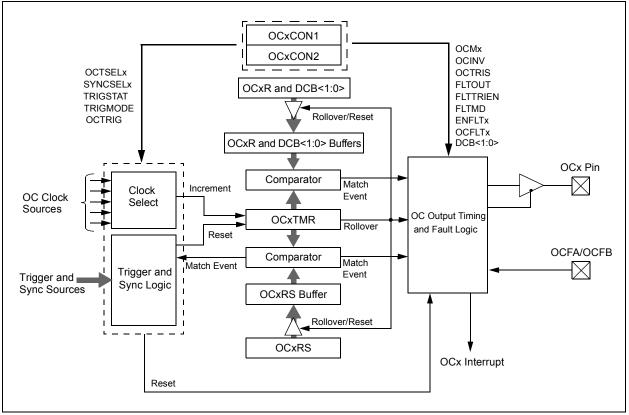

Figure 35-1 illustrates the block diagram of the output compare module.

**Note:** For complete information on the number of available channels, refer to the specific device data sheet.

All of the output compare channels are functionally identical. In this section, an 'x' in the pin, register or bit name denotes the specific output compare channel.

The OCx output must be assigned to an available RPn pin before use if the device supports Peripheral Pin Select (PPS). Refer to the Peripheral Pin Select section in the data sheet for more information.

# 35.2 OUTPUT COMPARE REGISTERS

Each output compare channel is comprised of the following registers:

- · OCxCON1 and OCxCON2 Control registers for the output compare channel

- OCxR Data register for the output compare channel

- · OCxRS Secondary Data register for the output compare channel

- OCxTMR The Internal Time Base register

The control registers for the output compare channels are named OC1CON1 and OC1CON2 through OCnCON1 and OCnCON2, where 'n' is the number of OC modules present in the device.

All the control registers have identical bit definitions. They can be represented by common register definitions as listed in Register 35-1 through Register 35-5. The 'x' in the register names represents the output compare channel number.

| U-0             | U-0                                                                                                                                                         | R/W-0                               | R/W-0                 | R/W-0               | R/W-0                        | R/W-0                        | R/W-0                        |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|---------------------|------------------------------|------------------------------|------------------------------|--|--|--|

|                 | _                                                                                                                                                           | OCSIDL                              | OCTSEL2               | OCTSEL1             | OCTSEL0                      | ENFLT2 <sup>(3)</sup>        | ENFLT1 <sup>(3)</sup>        |  |  |  |

| bit 15          |                                                                                                                                                             | •                                   | •                     |                     |                              |                              | bit 8                        |  |  |  |

| R/W-0           | R/W-0, HCS                                                                                                                                                  | R/W-0, HCS                          | R/W-0, HCS            | DAMO                |                              | R/W-0                        |                              |  |  |  |

|                 | OCFLT2 <sup>(3)</sup>                                                                                                                                       | OCFLT1 <sup>(3)</sup>               |                       | R/W-0               | R/W-0<br>OCM2 <sup>(1)</sup> | R/W-0<br>OCM1 <sup>(1)</sup> | R/W-0<br>OCM0 <sup>(1)</sup> |  |  |  |

| ENFLT0<br>bit 7 | UCFLI2(*)                                                                                                                                                   | OCFLING                             | OCFLT0                | TRIGMODE            | UCMZ("                       | OCMIN                        | bit (                        |  |  |  |

|                 |                                                                                                                                                             |                                     |                       |                     |                              |                              |                              |  |  |  |

| Legend:         |                                                                                                                                                             | HCS = Hardw                         | are Clearable/        |                     |                              |                              |                              |  |  |  |

| R = Readable    |                                                                                                                                                             | W = Writable                        | bit                   | U = Unimplem        | ented bit, read              | l as '0'                     |                              |  |  |  |

| -n = Value at   | POR                                                                                                                                                         | '1' = Bit is set                    |                       | '0' = Bit is clea   | red                          | x = Bit is unkn              | iown                         |  |  |  |

| bit 15-14       | Unimplement                                                                                                                                                 | ted: Read as '                      | ר <b>י</b>            |                     |                              |                              |                              |  |  |  |

| bit 13          | -                                                                                                                                                           |                                     | are x in Idle Mo      | ode Control bit     |                              |                              |                              |  |  |  |

|                 | -                                                                                                                                                           |                                     | in CPU Idle mo        |                     |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             |                                     |                       | in CPU Idle mo      | ode                          |                              |                              |  |  |  |

| bit 12-10       | -                                                                                                                                                           | -                                   | ipare x Clock S       |                     |                              |                              |                              |  |  |  |

|                 | 111 = Periphe                                                                                                                                               | eral clock (Fcy                     | )                     |                     |                              |                              |                              |  |  |  |

|                 | 110 = Reserved                                                                                                                                              |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 101 = Reserved                                                                                                                                              |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 100 = Timer1 clock (only synchronous clock is supported)                                                                                                    |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 011 = Timer5 clock<br>010 = Timer4 clock                                                                                                                    |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 001 = Timer3                                                                                                                                                |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 000 = Timer2 clock                                                                                                                                          |                                     |                       |                     |                              |                              |                              |  |  |  |

| bit 9           | ENFLT2: Fau                                                                                                                                                 | lt 2 Input Enab                     | le bit <sup>(3)</sup> |                     |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             | ts are enabled                      |                       |                     |                              |                              |                              |  |  |  |

|                 | •                                                                                                                                                           | ts are disabled                     |                       |                     |                              |                              |                              |  |  |  |

| bit 8           | ENFLT1: Fault 1 Input Enable bit <sup>(3)</sup>                                                                                                             |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 1 = Fault inputs are enabled                                                                                                                                |                                     |                       |                     |                              |                              |                              |  |  |  |

| bit 7           | <ul> <li>0 = Fault inputs are disabled</li> <li>ENFLT0: Fault 0 Input Enable bit (corresponds to OCFA pin)</li> <li>1 = Fault inputs are enabled</li> </ul> |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 | 0 = Fault inpu                                                                                                                                              | uts are disable                     | b                     | <i>(</i> <b>-</b> ) |                              |                              |                              |  |  |  |

| bit 6           |                                                                                                                                                             |                                     | dition Status bit     | (3)                 |                              |                              |                              |  |  |  |

|                 | 1 = PWM Fault condition has occurred                                                                                                                        |                                     |                       |                     |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             | Fault condition                     |                       | (2)                 |                              |                              |                              |  |  |  |

| bit 5           |                                                                                                                                                             |                                     | dition Status bit     | (3)                 |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             | It condition has<br>Fault condition |                       |                     |                              |                              |                              |  |  |  |

| bit 4           |                                                                                                                                                             |                                     | dition Status bit     |                     |                              |                              |                              |  |  |  |

| 511 -           |                                                                                                                                                             | ult condition ha                    |                       |                     |                              |                              |                              |  |  |  |

|                 |                                                                                                                                                             | Fault condition                     |                       |                     |                              |                              |                              |  |  |  |

| bit 3           |                                                                                                                                                             |                                     | Mode Select bi        | t                   |                              |                              |                              |  |  |  |

| · -             | 1 = TRIGSTA                                                                                                                                                 |                                     | <6>) is cleared       | when OCxRS =        | OCxTMR or i                  | n software                   |                              |  |  |  |

|                 |                                                                                                                                                             |                                     | , . ,                 |                     |                              |                              |                              |  |  |  |

## Register 35-1: OCxCON1: Output Compare x Control Register 1

- **Note 1:** The OCx output must also be configured to an available RPn pin if the device supports Peripheral Pin Select (PPS). For more information, refer to the specific device data sheet.

- 2: OCxR and OCxRS are double-buffered only in PWM modes.

- **3:** Refer to the device data sheet to find the Fault bits mapping.

## Register 35-1: OCxCON1: Output Compare x Control Register 1 (Continued)

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits<sup>(1)</sup>

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(2)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(2)</sup>

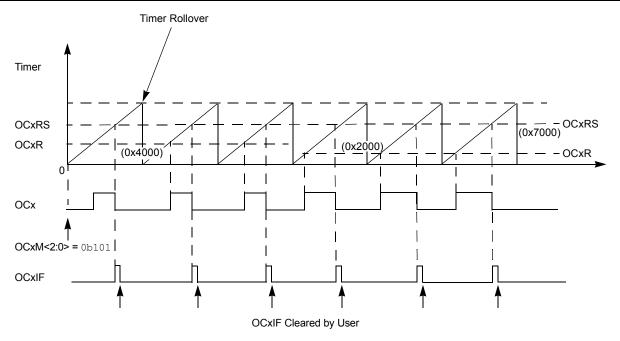

- 101 = Double Compare Continuous Pulse mode: Initialize OCx pin low, toggle OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initialize OCx pin low, toggle OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare events with OCxR, continuously toggle OCx pin

- 010 = Single Compare Single-Shot mode: Initialize OCx pin high, compare event with OCxR; forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initialize OCx pin low, compare event with OCxR; forces OCx pin high

- 000 = Output compare channel is disabled

- **Note 1:** The OCx output must also be configured to an available RPn pin if the device supports Peripheral Pin Select (PPS). For more information, refer to the specific device data sheet.

- 2: OCxR and OCxRS are double-buffered only in PWM modes.

- 3: Refer to the device data sheet to find the Fault bits mapping.

| Register 35- |                                                                                                                         |                                                                                                                                                            | pare x Contro                                                                                                                            | -                                                                                                                                                 |                                                                                      |                                     |              |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------|--------------|--|--|

| R/W-0        | R/W-0                                                                                                                   | R/W-0                                                                                                                                                      | R/W-0                                                                                                                                    | U-0                                                                                                                                               | R/W-0                                                                                | R/W-0                               | R/W-0        |  |  |

| FLTMD        | FLTOUT                                                                                                                  | FLTTRIEN                                                                                                                                                   | OCINV                                                                                                                                    | —                                                                                                                                                 | DCB1 <sup>(3)</sup>                                                                  | DCB0 <sup>(3)</sup>                 | OC32         |  |  |

| bit 15       |                                                                                                                         |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     | bit 8        |  |  |

| R/W-0        | R/W-0, HS                                                                                                               | R/W-0                                                                                                                                                      | R/W-0                                                                                                                                    | R/W-0                                                                                                                                             | R/W-0                                                                                | R/W-0                               | R/W-0        |  |  |

| OCTRIG       | TRIGSTAT                                                                                                                | OCTRIS                                                                                                                                                     | SYNCSEL4                                                                                                                                 | SYNCSEL3                                                                                                                                          | SYNCSEL2                                                                             | SYNCSEL1                            | SYNCSELC     |  |  |

| bit 7        |                                                                                                                         |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      | •                                   | bit          |  |  |

| Legend:      |                                                                                                                         | HS = Hardwa                                                                                                                                                | re Settable bit                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

| R = Readab   | le bit                                                                                                                  | W = Writable                                                                                                                                               | bit                                                                                                                                      | U = Unimplem                                                                                                                                      | nented bit, read                                                                     | l as '0'                            |              |  |  |

| -n = Value a | t POR                                                                                                                   | '1' = Bit is set                                                                                                                                           |                                                                                                                                          | '0' = Bit is clea                                                                                                                                 |                                                                                      | x = Bit is unkr                     | iown         |  |  |

| bit 15       | cleared in                                                                                                              | de is maintain<br>software and                                                                                                                             | ed until the Fa<br>a new PWM p                                                                                                           |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              |                                                                                                                         |                                                                                                                                                            | d until the Fau                                                                                                                          | It source is rem                                                                                                                                  | loved and a ne                                                                       | w PWM period                        | starts       |  |  |

| bit 14       | FLTOUT: Faul                                                                                                            |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              | 1 = PWM out<br>0 = PWM out                                                                                              |                                                                                                                                                            | 0                                                                                                                                        |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

| bit 13       | -                                                                                                                       |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              | FLTTRIEN: Fault Output State Select bit<br>1 = OCx pin is tri-stated on Fault condition                                 |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              | 0 = OCx pin l                                                                                                           | /O state define                                                                                                                                            | d by FLTOUT                                                                                                                              | bit on Fault con                                                                                                                                  | dition                                                                               |                                     |              |  |  |

| bit 12       | OCINV: OCM                                                                                                              | P Invert bit                                                                                                                                               |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              | 1 = OCx outp<br>0 = OCx outp                                                                                            |                                                                                                                                                            | ed                                                                                                                                       |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

| bit 11       | Unimplement                                                                                                             |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

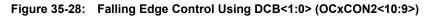

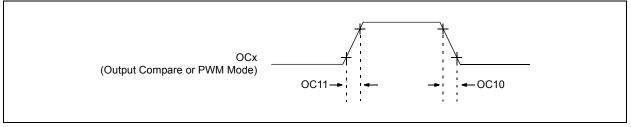

| bit 10-9     | These bits can<br>Generation more<br>rising edge wh<br>00 = OCx outp<br>01 = OCx outp<br>10 = OCx outp<br>11 = OCx outp | n be considered<br>odes. They are<br>nen output inver-<br>out falling edge<br>out falling edge<br>out falling edge<br>out falling edge<br>out falling edge | e also used to o<br>ersion is active<br>e transitions on<br>e transitions on<br>e transitions on<br>e transitions on<br>e transitions on | Least Significar<br>delay the falling<br>(OCINV (OCXC<br>rising edge of<br>rising edge of<br>rising edge of<br>rising edge of<br>resolution of (I | edge of the O<br>CON2<12> = 1)<br>P1 clock (Lega<br>P2 clock<br>P3 clock<br>P4 clock | Cx output in all<br>).<br>icy mode) | l other mode |  |  |

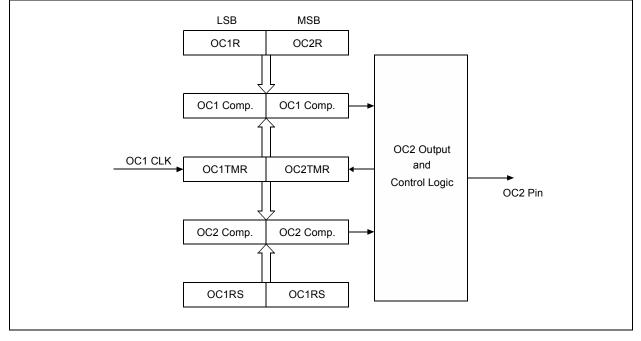

| bit 8        | OC32: Cascad                                                                                                            | de Two OCx N                                                                                                                                               | Iodules Enable                                                                                                                           | bit (32-bit oper                                                                                                                                  | ration)                                                                              | —                                   |              |  |  |

|              | 1 = Cascade                                                                                                             |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

| L:1 7        | 0 = Cascade                                                                                                             |                                                                                                                                                            |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

| bit 7        |                                                                                                                         | Cx from sourc                                                                                                                                              | e designated b                                                                                                                           | y SYNCSELx b                                                                                                                                      |                                                                                      |                                     |              |  |  |

| bit 6        | TRIGSTAT: Ti                                                                                                            |                                                                                                                                                            | -                                                                                                                                        | ted by SYNCSI                                                                                                                                     |                                                                                      |                                     |              |  |  |

|              |                                                                                                                         |                                                                                                                                                            | triggered and is                                                                                                                         | s running                                                                                                                                         |                                                                                      |                                     |              |  |  |

|              |                                                                                                                         |                                                                                                                                                            |                                                                                                                                          | nd is being held                                                                                                                                  | d clear                                                                              |                                     |              |  |  |

| bit 5        |                                                                                                                         |                                                                                                                                                            | irection Select                                                                                                                          | •                                                                                                                                                 |                                                                                      |                                     |              |  |  |

|              | 1 = OCx is tri-                                                                                                         | -stated                                                                                                                                                    |                                                                                                                                          |                                                                                                                                                   |                                                                                      |                                     |              |  |  |

|              | 0 = Output co                                                                                                           | mpare module                                                                                                                                               | e drives the OC                                                                                                                          | x pin                                                                                                                                             |                                                                                      |                                     |              |  |  |

|              | ver use an OCx r<br>NCSEL settings.                                                                                     | module as its c                                                                                                                                            | own trigger sou                                                                                                                          | rce, either by s                                                                                                                                  | electing this mo                                                                     | ode or other eq                     | uivalent     |  |  |

| 3: The       | e these inputs as<br>e DCB<1:0> (OC<br>CM<2:0> (OCxC0                                                                   | xCON2<10:9>                                                                                                                                                | ) bits are doub                                                                                                                          |                                                                                                                                                   |                                                                                      | s only                              |              |  |  |

Register 35-2: OCxCON2: Output Compare x Control Register 2<sup>(4)</sup>

| Register 35-2 | : OCxCON2: Output Compare x Control Register 2 <sup>(4)</sup> (Continued) |

|---------------|---------------------------------------------------------------------------|

| bit 4-0       | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits               |

|               | 11111 = This OCx module <sup>(1)</sup>                                    |

|               | 11110 = Input Capture 9 <sup>(2)</sup>                                    |

|               | 11101 = Input Capture 6 <sup>(2)</sup>                                    |

|               | $11100 = CTMU^{(2)}$                                                      |

|               | $11011 = A/D^{(2)}$                                                       |

|               | 11010 = Comparator $3^{(2)}$                                              |

|               | 11001 = Comparator $2^{(2)}$                                              |

|               | 11000 = Comparator $1^{(2)}$                                              |

|               | 10111 - Input Conture 4(2)                                                |

- 10111 = Input Capture 4<sup>(2)</sup> 10110 = Input Capture 3<sup>(2)</sup>

- 10101 = Input Capture 2<sup>(2)</sup>

- 10100 = Input Capture 1<sup>(2)</sup>

- 10011 = Input Capture 8<sup>(2)</sup>

- 10010 = Input Capture 7<sup>(2)</sup>

- 1000x = Reserved

- 01111 = Timer5

- 01110 = Timer4

- 01101 = Timer3

- 01100 = Timer2

- 01011 = Timer1

- 01010 = Input Capture 5<sup>(2)</sup>

- 01001 = Output Compare 9

- 01000 = Output Compare 8

- 00111 = Output Compare 7

- 00110 = Output Compare 6

- 00101 = Output Compare 5

- 00100 = Output Compare 4

- 00011 = Output Compare 3

- 00010 = Output Compare 2

- 00001 = Output Compare 1

- 00000 = Not synchronized to any other module

- Note 1: Never use an OCx module as its own trigger source, either by selecting this mode or other equivalent SYNCSEL settings.

- 2: Use these inputs as trigger sources only and not as Sync sources.

- 3: The DCB<1:0> (OCxCON2<10:9>) bits are double-buffered in the PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

- 4: Refer to the specific device data sheet to check if these bits are supported in the device.

#### Register 35-3: OCxR: Compare Register

| OCRB15 OCRB14 OCRB13 OCRB12 OCRB11 OCRB10 OCRB9 |       |

|-------------------------------------------------|-------|

|                                                 | OCRB8 |

| bit 15                                          | bit 8 |

| R/W-0 | R/W-0, HS | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----------|-------|-------|-------|-------|-------|-------|

| OCRB7 | OCRB6     | OCRB5 | OCRB4 | OCRB3 | OCRB2 | OCRB1 | OCRB0 |

| bit 7 |           |       |       |       |       |       | bit 0 |

| Legend:           | HS = Hardware Settable bit |                             |                    |  |  |

|-------------------|----------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | as '0'             |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0 OCRB<15:0>: Primary Compare Register Value bits When OCM<2:0> = 0b110: This register is used for the duty cycle in an edge-aligned PWM. When OCM<2:0> = 0b111, 0b101, 0b100: This register is used for generating a positive edge. When OCM<2:0> = 0b001, 0b010, 0b011: This register is used for generating all edges.

| Register 35-4: | OCxRS: Secondary | Compare Register |

|----------------|------------------|------------------|

|----------------|------------------|------------------|

| R/W-0   | R/W-0     | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

|---------|-----------|---------|---------|---------|---------|--------|--------|

| OCRSB15 | OCRSB14   | OCRSB13 | OCRSB12 | OCRSB11 | OCRSB10 | OCRSB9 | OCRSB8 |

| bit 15  |           |         |         |         |         |        | bit 8  |

|         |           |         |         |         |         |        |        |

| R/W-0   | R/W-0, HS | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  |

| OCRSB7  | OCRSB6    | OCRSB5  | OCRSB4  | OCRSB3  | OCRSB2  | OCRSB1 | OCRSB0 |

| bit 7   |           |         |         |         |         |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-0

OCRSB<15:0>: Secondary Compare Register Value bits

This is the Period register:

If OCxCON2 (SYNCSEL<4:0>) = 0x1F

If OCxCON2 (SYNCSEL<4:0>) = N (where N is the alternate value to select this as the Period register)

If OCxCON2 (OCTRIG = 1)

All other conditions:

The period is determined outside this module. Used for generating a negative edge when OCM<2:0> = 0b111, 0b101 or 0b100.

# Section 35. Output Compare with Dedicated Timer

|                                   | Timer Register | r                                                            |                                                              |                                                                                                                                                            |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                           |

|-----------------------------------|----------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R-0                               | R-0            | R-0                                                          | R-0                                                          | R-0                                                                                                                                                        | R-0                                                                                                                                                                                                    | R-0                                                                                                                                                                                                                                                                                       |

| TMRB14                            | TMRB13         | TMRB12                                                       | TMRB11                                                       | TMRB10                                                                                                                                                     | TMRB9                                                                                                                                                                                                  | TMRB8                                                                                                                                                                                                                                                                                     |

|                                   |                |                                                              |                                                              |                                                                                                                                                            |                                                                                                                                                                                                        | bit 8                                                                                                                                                                                                                                                                                     |

|                                   |                |                                                              |                                                              |                                                                                                                                                            |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                           |

| R-0                               | R-0            | R-0                                                          | R-0                                                          | R-0                                                                                                                                                        | R-0                                                                                                                                                                                                    | R-0                                                                                                                                                                                                                                                                                       |

| TMRB6                             | TMRB5          | TMRB4                                                        | TMRB3                                                        | TMRB2                                                                                                                                                      | TMRB1                                                                                                                                                                                                  | TMRB0                                                                                                                                                                                                                                                                                     |

|                                   |                |                                                              |                                                              |                                                                                                                                                            |                                                                                                                                                                                                        | bit 0                                                                                                                                                                                                                                                                                     |

|                                   |                |                                                              |                                                              |                                                                                                                                                            |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                           |

| R = Readable bit W = Writable bit |                | bit                                                          | U = Unimplemented bit, read as '0'                           |                                                                                                                                                            |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                           |

| -n = Value at POR '1' = E         |                |                                                              | '0' = Bit is clea                                            | ared                                                                                                                                                       | x = Bit is unkr                                                                                                                                                                                        | nown                                                                                                                                                                                                                                                                                      |

|                                   | R-0<br>TMRB6   | TMRB14 TMRB13<br>R-0 R-0<br>TMRB6 TMRB5<br>it W = Writable t | TMRB14TMRB13TMRB12R-0R-0R-0TMRB6TMRB5TMRB4itW = Writable bit | TMRB14     TMRB13     TMRB12     TMRB11       R-0     R-0     R-0       TMRB6     TMRB5     TMRB4     TMRB3       it     W = Writable bit     U = Unimplem | TMRB14     TMRB13     TMRB12     TMRB11     TMRB10       R-0     R-0     R-0     R-0       TMRB6     TMRB5     TMRB4     TMRB3     TMRB2       it     W = Writable bit     U = Unimplemented bit, read | TMRB14       TMRB13       TMRB12       TMRB11       TMRB10       TMRB9         R-0       R-0       R-0       R-0       R-0       R-0         TMRB6       TMRB5       TMRB4       TMRB3       TMRB2       TMRB1         it       W = Writable bit       U = Unimplemented bit, read as '0' |

bit 15-0 **TMRB<15:0>:** Ouput Compare x Timer bits The current value of the Output Compare x Timer.

# 35.3 MODES OF OPERATION

Each output compare module comprises the following modes of operation:

- Single Compare Match mode

- Dual Compare Match mode generating:

- Single output pulse

- Continuous output pulse

- Simple Pulse-Width Modulation mode with/without Fault protection:

- Edge-aligned

- Center-aligned

- Cascade mode (32-bit operation)

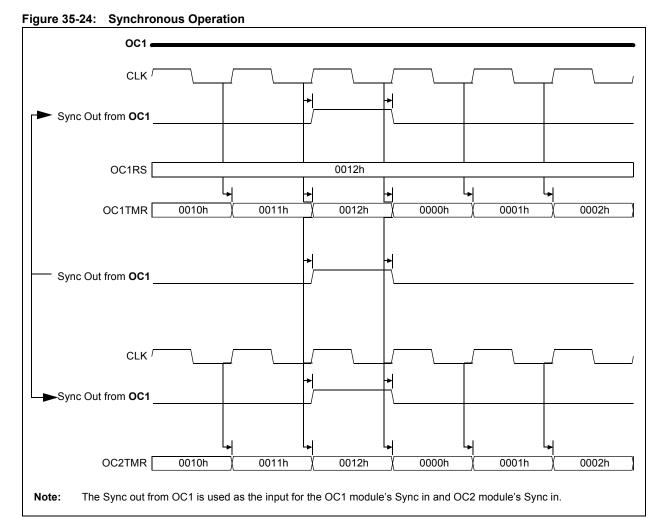

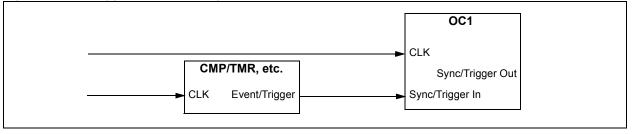

Before understanding the modes, it is necessary to understand the synchronization/trigger mechanism. In synchronous operation, the internal timer is reset (to zero) when the source selected by the SYNCSEL<4:0> (OCxCON2<4:0>) bits sends a Sync signal. In Trigger mode, the internal timer is held in the Reset state until the selected trigger source sends a Sync signal.

The Synchronous or Trigger mode is selected by the OCTRIG (OCxCON2<7>) bit and the synchronization/trigger source can be selected by the SYNCSEL<4:0> (OCxCON2<4:0>) bits, as indicated in **Section 35.2 "Output Compare Registers"**.

| Note: | SYNCSEL<4:0> (OCxCON2<4:0>) = 0b00000 puts the timer in a Free-Running mode with no synchronization.                                           |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

|       | SYNCSEL<4:0> (OCxCON2<4:0>) = 0b11111 makes the timer reset when it reaches the value of OCxRS, making the OCx module use its own Sync signal. |

|       | OCx module sends out a synchronization/trigger signal when its timer matches OCxRS.                                                            |

For more information on Synchronous/Trigger mode, refer to **Section 35.3.3.7** "Synchronous **Operation**".

# 35.3.1 Single Compare Match Mode

When control bits, OCM<2:0> (OCxCON1<2:0>) = 0b001, 0b010 or 0b011, the selected output compare channel is configured as:

- If OCM<2:0> (OCxCON1<2:0>) = 0b001: The OCx pin is initially set low; a subsequent compare event with OCxR sets the pin high

- If OCM<2:0> (OCxCON1<2:0>) = 0b010: The OCx pin is initially set high; a subsequent compare event with OCxR sets the pin low

- If OCM<2:0> (OCxCON1<2:0>) = 0b011: The OCx pin is initially set low, a subsequent compare event with OCxR toggles the pin

In Single Compare mode, the OCxR register is used to generate compare events. This register is loaded with a value and is compared with the module Timer register. The interrupt is set on each compare event if there is a level change in the OCx pin.

## 35.3.1.1 SINGLE COMPARE MODE OUTPUT DRIVEN HIGH

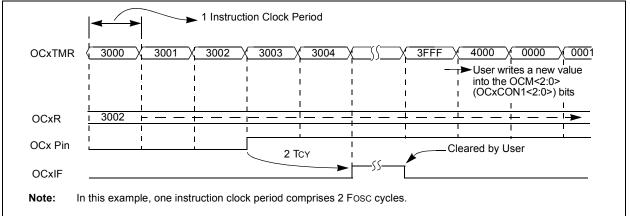

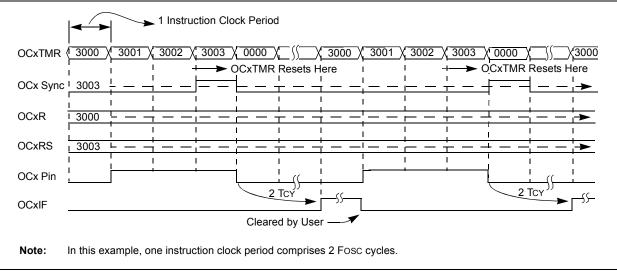

To configure the module for this mode, set control bits, OCM<2:0> (OCxCON1<2:0>) = 0b001. Once this Compare mode is enabled, the output pin, OCx, will be initially driven low and remain low until a match between the timer and the OCxR registers occurs. Figure 35-2 provides the following key timing events:

- The OCx pin is driven high one instruction clock after a compare match between the timer and the OCxR register. The OCx pin remains high until a mode change or the module is turned off.

- The timer counts up until it rolls over, or a synchronization event occurs, and then resets (to 0x0000) on the next instruction clock.

- The respective channel interrupt flag, OCxIF, is asserted two instruction clocks after the OCx pin is driven high.

Figure 35-2: Single Compare Mode – Set OCx High on Compare Match Event

# 35.3.1.2 SINGLE COMPARE MODE OUTPUT DRIVEN LOW

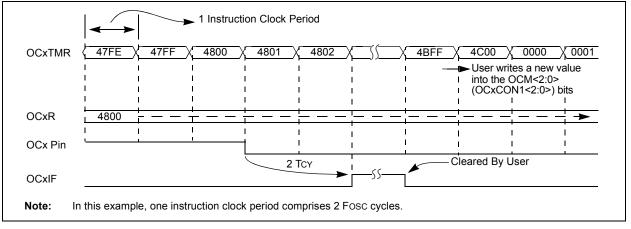

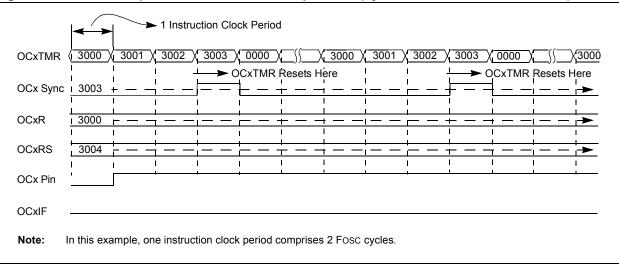

To configure the output compare module for this mode, set control bits, OCM<2:0> (OCxCON1<2:0>) = 0b010. Once this Compare mode is enabled, the output pin and the OCx will be initially driven high and remain high until a match occurs between the Timer and the OCxR registers. Figure 35-3 provides the key timing events.

- The OCx pin is driven low one instruction clock after a compare match event occurs between the timer and the OCxR register. The OCx pin remains low until a mode change or the module is turned off.

- The timer counts up until it rolls over or a synchronization event occurs, and then resets to 0x0000 on the next instruction clock.

- The respective channel interrupt flag, OCxIF, is asserted two instruction clocks after the OCx pin is driven low.

#### Figure 35-3: Single Compare Mode – Force OCx Low on Compare Match Event

Output Compare wif

### 35.3.1.3 SINGLE COMPARE MODE TOGGLE OUTPUT

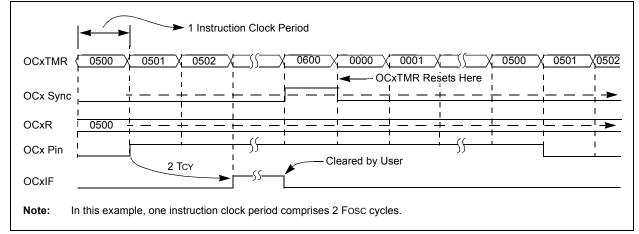

To configure the output compare module for this mode, set control bits, OCM<2:0> (OCxCON1<2:0>) = 0b011. Once this Compare mode has been enabled, the output pin and the OCx toggle on every match event between the timer and the OCxR registers. Figure 35-4 provides the key timing events.

- The OCx pin is toggled one instruction clock after a compare match occurs between the timer and OCxR register. The OCx pin remains at this new state until the next toggle event, or until a mode change has been made or the module is turned off.

- The timer counts up until it rolls over or synchronization occurs and then resets to 0x0000 on the next instruction clock.

- The respective channel interrupt flag, OCxIF, is asserted two instruction clocks after the OCx pin is toggled.

- The internal OCx pin output logic is set to a logic '0' on a device Reset. However, the operational OCx pin state for the Toggle mode can be set by the user software.

#### Example 35-1: Single Compare Mode Toggle Output

| OC1CON1 = 0;             | /* It is a good practice to clear off the control bits initially */ |

|--------------------------|---------------------------------------------------------------------|

| OC1CON2 = 0;             |                                                                     |

| OC1CON1bits.OCTSEL = 0x0 | 7;/* This selects the peripheral clock as the clock input to the OC |

|                          | module */                                                           |

| OC1R = 1000;             | /* This is just a typical number, user must calculate based on the  |

|                          | waveform requirements and the system clock */                       |

| OC1CON1bits.OCM = 3;     | /* This selects and starts the toggle mode $*/$                     |

|                          |                                                                     |

# 35.3.1.4 SPECIAL CASES OF SINGLE COMPARE MODE

Consider the following few special cases:

#### Table 35-1: Special Cases of Single Compare Mode

| Special Condition                                                                                                                        | Operation                                                                                                                                                                 | Output                            |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| When OCxR > timer period (as determined<br>by the Sync source)                                                                           | No compare event occurs and the<br>compare output remains at the initial<br>condition.                                                                                    | No change in output level         |

| When OCxR = timer period (as determined by the Sync source)                                                                              | The compare output functions normally.<br>Combining this with the Toggle mode can<br>be used to generate a fixed frequency<br>square wave, as illustrated in Figure 35-5. | Output level transition           |

| When the module is enabled into a Single<br>Compare mode (OCxR = 0x0000) and the<br>timer is held in Reset, the Sync source is<br>active | The compare output remains in the initial condition.                                                                                                                      | No change in output level         |

| If, after a compare event, the OCxR register is cleared and the Sync source becomes active                                               | Output remains in the new state.                                                                                                                                          | No further change in output level |

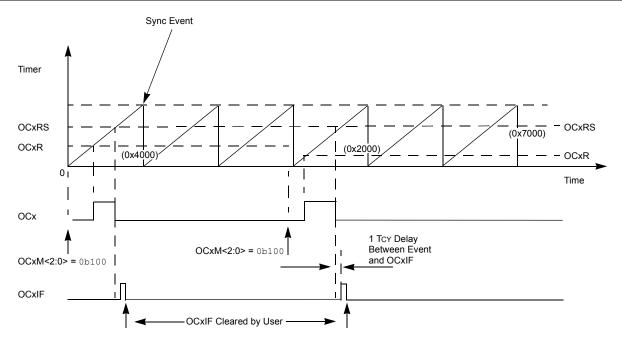

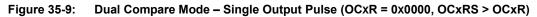

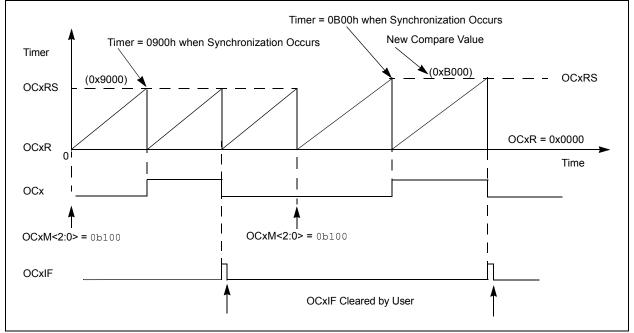

# 35.3.2 Dual Compare Match Mode

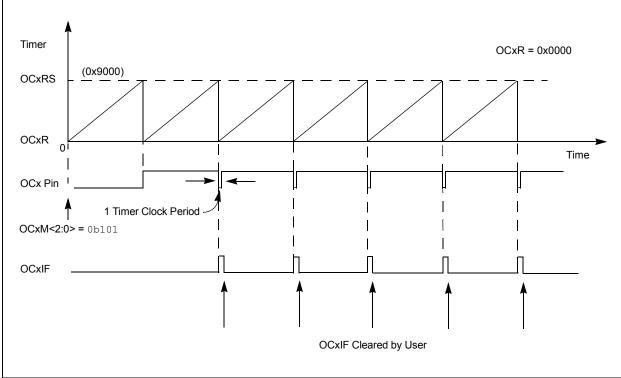

When control bits, OCM<2:0> (OCxCON1<2:0>) = 0b100 or 0b101, the selected output compare channel is configured for one of the two following Dual Compare Match modes:

- Single Output Pulse mode

- Continuous Output Pulse mode

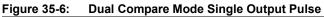

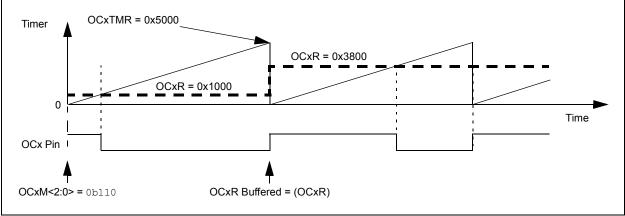

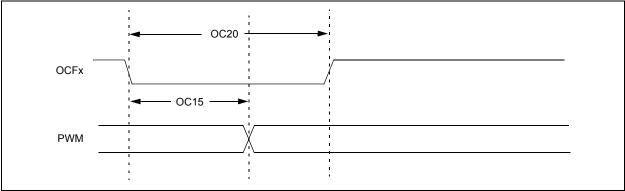

In the Dual Compare mode, the module uses both the OCxR and OCxRS registers for the compare match events. The OCxR register is compared with the incrementing timer count, OCxTMR, and the rising (leading) edge of the pulse is generated at the OCx pin on a compare match event. The OCxRS register is then compared to the same incrementing timer count, OCxTMR, and the falling (trailing) edge of the pulse is generated at the OCx pin on a compare match event.

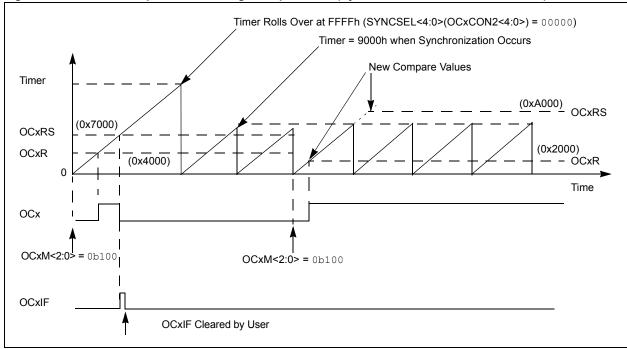

### 35.3.2.1 DUAL COMPARE SINGLE PULSE MODE

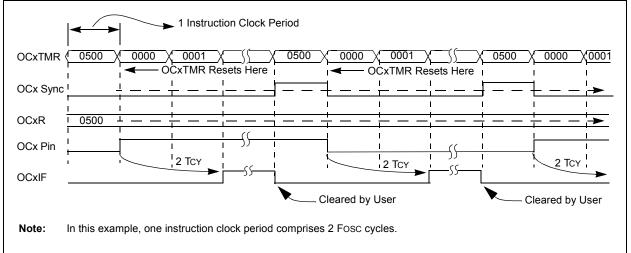

When control bits, OCM<2:0> (OCxCON1<2:0>) = 0b100, the selected output compare channel is configured so that the OCx pin is initialized low and a single output pulse is generated. Refer to Figure 35-6 and Figure 35-7.

- 1. Once the Dual Compare Single Pulse mode is enabled, the OCx pin will be driven low.

- 2. Upon the first timer compare match with OCxR, the Compare register, its pin (OCx) would be driven high.

- 3. When the incrementing timer count matches the Compare register, OCxRS, the second and trailing edge (high-to-low) of the pulse is driven onto the OCx pin. At this second compare, the OCxIF interrupt flag bit gets set.

- **Note:** While the mode bits do not change after the falling edge of the pulse, if another write with the same value occurs on the same control bits, a new single output pulse sequence is generated.

- The value of OCxRS must be greater than the OCxR by a minimum of 2.

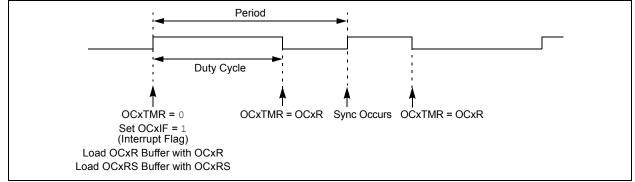

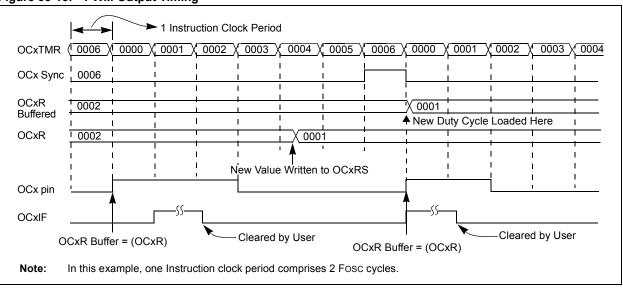

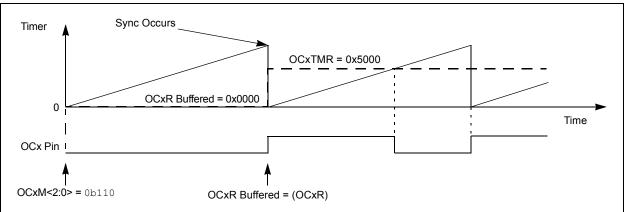

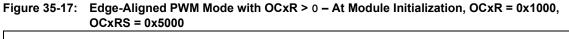

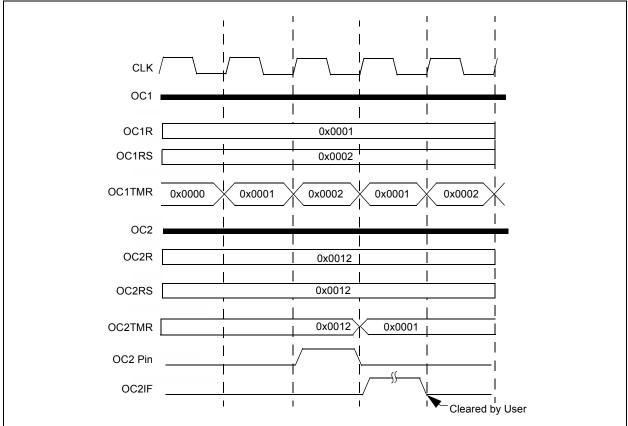

## Figure 35-7: Dual Compare Mode

# 35.3.2.2 TO SET UP SINGLE OUTPUT PULSE GENERATION

To configure the module for the generation of a single output pulse, perform the following steps:

- 1. Determine the instruction cycle time, Tcy.

- 2. Calculate the desired pulse-width value base upon Tcy.

- 3. Calculate the time to start pulse from timer start value of 0x0000.

- 4. Write pulse-width start and stop times into OCxR and OCxRS Compare registers.

- 5. Select SYNCSEL<4:0> (OCxCON2<4:0>) so that the synchronization is active after the timer is equal to, or greater than, the value in OCxRS.

- 6. Set OCM<2:0> (OCxCON1<2:0>) = 0b100; the pulse will be generated.

- 7. Issue another write to set OCM<2:0> (OCxCON1<2:0>) = 0b100 to initiate another single pulse with the same parameters.

- 8. Disable the OCx by writing OCM<2:0> (OCxCON1<2:0>) = 0b000 to change the parameters, and then enable the OCx by writing OCM<2:0> (OCxCON1<2:0>) = 0b100 to initiate another single pulse with different parameters.

Note: Refer to Table 35-2 for several simple examples of single output pulse-width calculations.

Refer to Table 35-4 for several simple examples of Dual Compare Match mode generating a single output pulse.

#### Table 35-2: Dual Compare Mode – Single Output Pulse-Width Calculation Examples

| Instruction Cycle | Desired | d on Time |        | e Time from<br>= 0x0000 | End Pulse Time   |

|-------------------|---------|-----------|--------|-------------------------|------------------|

| Time (TCY)        | Time    | Value     | Time   | Value<br>(OCxR)         | (OCxRS) Register |

| 62.5 ns           | 3 μs    | 0x0030    | 10 μs  | 0x00A0                  | 0x0D0            |

| 100 ns            | 5 μs    | 0x0032    | 10 μs  | 0x0064                  | 0x0096           |

| 300 ns            | 10 μs   | 0x0021    | 100 μs | 0x014D                  | 0x018F           |

| 500 ns            | 20 μs   | 0x0028    | 500 μs | 0x03E8                  | 0x0410           |

| 500 ns            | 30 μs   | 0x003C    | 2 ms   | 0x0FA0                  | 0x0FDC           |

#### Equation 35-1:

Value = Desired Time/Instruction Cycle Time (TCY)

| 1 | Example 35-2: Dual Compar             | e Mode – Single Output Pulse Width                                                                                       |

|---|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|   | OC1CON1 = 0;<br>OC1CON2 = 0;          | /* It is a good practice to clear off the control bits initially */                                                      |

|   | OC1CON1bits.OCTSEL = 0x07;            | /* This selects the peripheral clock as the clock input to the OC module $^{\prime\prime}$                               |

|   | OC1R = 1000;                          | /* This is just a typical number, user must calculate based on the waveform requirements and the system clock $^{\ast/}$ |

|   | OC1RS = 2000;<br>OC1CON1bits.OCM = 4; | /* This selects and starts the Single Output Pulse mode $^{\prime}$                                                      |

# Example 35-2: Dual Compare Mode – Single Output Pulse Width

# Table 35-3: Special Cases for Dual Compare Match Mode Generating a Single Output Pulse

| Special Condition                                                                      | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output                                          |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Synchronization occurs when the timer value is equal to OCxRS                          | Timer resets to zero in the next cycle, but the pulse is unaffected.                                                                                                                                                                                                                                                                                                                                                                                                    | Pulse                                           |

| Synchronization occurs before the timer value reaches OCxR                             | Timer resets to zero before any output transition.                                                                                                                                                                                                                                                                                                                                                                                                                      | Remains low                                     |

| Synchronization occurs before the timer value reaches OCxRS, but after it reaches OCxR | Only a single transition (low-to-high) is generated (see Figure 35-8).                                                                                                                                                                                                                                                                                                                                                                                                  | Low/High                                        |

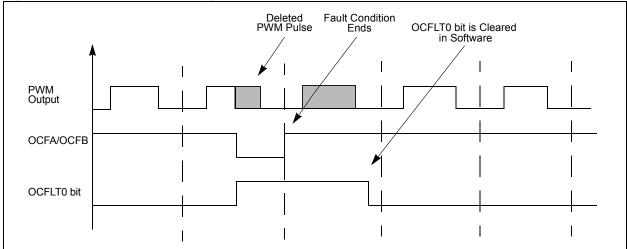

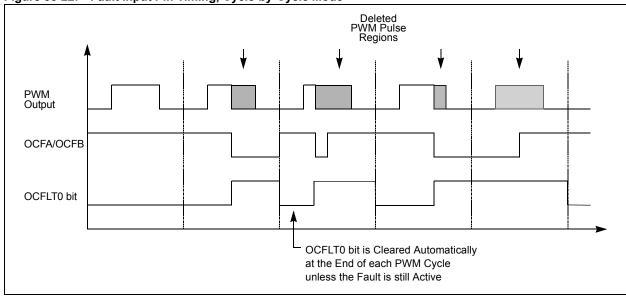

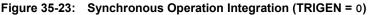

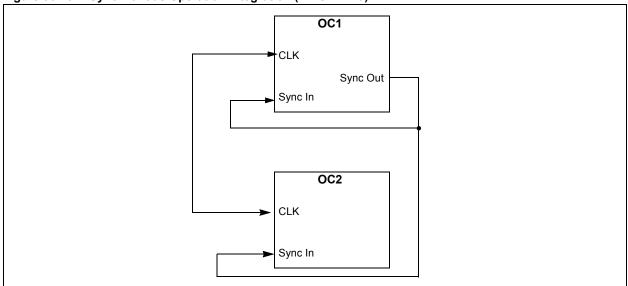

| OCxR = OCxRS = 0x0000 and<br>Sync occurs                                               | The output is initialized low and does not change. No interrupt is generated.                                                                                                                                                                                                                                                                                                                                                                                           | Remains low                                     |